© 2018 ІМФ (Інститут металофізики ім. Г. В. Курдюмова НАН України) Надруковано в Україні. Фотокопіювання дозволено тільки відповідно до ліцензії

PACS numbers: 72.20.Dp, 72.80.Ey, 85.30.De, 85.30.Pq, 85.30.Tv, 85.40.Bh

# Физика нанотранзисторов: теория MOSFET в традиционном изложении, начала модели виртуального истока и приближение истощения

Ю. А. Кругляк

Одесский государственный экологический университет, ул. Львовская, 15, 65016 Одесса, Украина

Рассмотрена традиционная теория MOSFET. Обсуждаются лишь наиболее существенные идеи привычного подхода, получившего также название «сверху-вниз». В частности, ограничимся моделированием лишь линейной области и области насыщения вольт-амперных характеристик и вместе с тем покажем, что существенные черты традиционного подхода вполне приемлемы и могут служить отправной точкой при разработке во многом совершенно иной физической картины процессов в нанотранзисторах. Традиционная модель MOSFET была переписана в форме, близкой к модели виртуального истока. Применение этой усовершенствованной модели к современным нанотранзисторам оказалось удивительно удачным, что является следствием учёта электростатики MOS через такой существенный фактор как контроль высоты барьера между истоком и каналом со стороны затвора. Наиболее слабым местом этой модели является описание транспорта электронов, поскольку оно базируется на использовании таких понятий как подвижность и скорость насыщения. Именно поэтому эти две метрики и были выбраны в качестве подгоночных параметров, с целью вписаться в экспериментальные данные для входных характеристик. Далее мы вернёмся к более глубокому рассмотрению электростатики MOS и покажем, как можно более корректно описать подпороговую и надпороговую области, результатом чего явится улучшенная модель виртуального истока, однако подвижность и скорость насыщения всё же останутся подгоночными параметрами. После этого физически более корректно опишем транспорт электронов с учётом возможности баллистического транспорта и окончательно построим модель виртуального истока, адекватную современным нанотранзисторам с длиной канала проводимости не менее 10 нм.

Розглянуто традиційну теорію MOSFET. Обговорюються лише найістотніші ідеї звичного підходу, який отримав назву «зверху—вниз». Зокрема, обмежимося моделюванням лише лінійної области й области наситу вольтамперних характеристик і в той же час покажемо, що істотні риси тради-

ційного підходу цілком прийнятні та можуть стати відправною точкою при розробці багато в чому зовсім іншої фізичної картини процесів у нанотранзисторах. Традиційний модель MOSFET було переписано в формі, близькій до моделю віртуального витоку. Застосування цього вдосконаленого моделю до сучасних нанотранзисторів виявилося напрочуд вдалим, що є наслідком врахування електростатики MOS через такий істотний чинник як контроль висоти бар'єру між витоком і каналом з боку закривки. Найслабшим місцем цього моделю  $\epsilon$  опис транспорту електронів, оскільки він ґрунтується на використанні таких понять як рухливість і швидкість наситу. Саме тому ці дві метрики й було обрано в якості припасувальних параметрів з метою вписатися в експериментальні дані для вхідних характеристик. Далі ми повернемося до більш глибокого розгляду електростатики MOS і покажемо як можна більш коректно описати підпорогову та надпорогову області, результатом чого виявиться поліпшений модель віртуального витоку, однак рухливість і швидкість наситу все ж залишаться припасувальними параметрами. Після цього фізично більш коректно опишемо транспорт електронів з урахуванням можливости балістичного транспорту й остаточно побудуємо модель віртуального витоку, адекватний сучасним нанотранзисторам із довжиною каналу провідности не менше 10 нм.

The traditional theory of MOSFET is discussed. Only the most significant ideas of the traditional approach, which also received the 'top-down' label, are discussed. In particular, we shall confine ourselves by means of the simulating only the linear region and the saturation region of the current-voltage characteristics and, at the same time, show that the essential features of the traditional approach are quite acceptable and can serve as a starting point in the development of a completely different physical picture of processes in the nanotransistors. The traditional MOSFET model is rewritten in a form close to the virtual source model. The application of this improved model to modern nanotransistors is surprisingly successful that is a consequence of taking into account MOS electrostatics through such an important factor as controlling the height of the barrier between the source and the channel from the gate side. The weakest point of this model is the description of electron transport, because it is based on the use of such concepts as mobility and saturation velocity. That is why these two metrics are chosen as fitting parameters in order to fit to the experimental data for the output characteristics. Next, we return to a deeper examination of MOS electrostatics and show how to describe the subthreshold and above-threshold regions correctly as possible, resulting in an improved model of the virtual source. However, the mobility and saturation velocity will nevertheless remain as fitting parameters. After that, we will physically more correctly describe the transport of electrons taking into account the possibility of ballistic transport and finally describe a virtual source model adequate to modern nanotransistors with a conduction channel length of not less than 10 nm.

**Ключевые слова:** наноэлектроника, полевой транзистор, вольт-амперные характеристики, метрика транзисторов, управление транзисторами, виртуальный исток.

Ключові слова: наноелектроніка, польовий транзистор, вольт-амперні

характеристики, метрика транзисторів, управління транзисторами, віртуальний витік.

**Keywords:** nanoelectronics, field effect transistor, current-voltage characteristics, transistor metrics, transistor control, virtual source.

(Получено 15 мая 2018 г.)

#### 1. ВВЕДЕНИЕ

Теория MOSFET была разработана ещё в 60-х годах прошлого века [1-5] и хотя она получила существенное развитие, но и ныне основные черты моделирования транзисторов остались такими же, как и 50 лет назад. Настоящий обзор посвящён традиционному изложению теории MOSFET [6, 7]. Мы обсудим лишь наиболее существенные идеи привычного подхода, получившего также название «сверху-вниз». В частности, мы ограничимся моделированием линейной области и области насыщения вольтамперных характеристик (BAX). Более детальное и полное представление о классической теории MOSFET можно найти в учебниках [8, 9]. Позже мы рассмотрим существенно другой подход к теории MOSFET, более адекватный физике нанотранзисторов, и вместе с тем покажем его связь с традиционным подходом.

## 2. ТОК, ЗАРЯД И СКОРОСТЬ

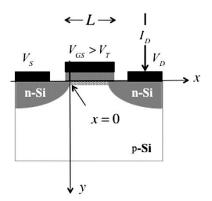

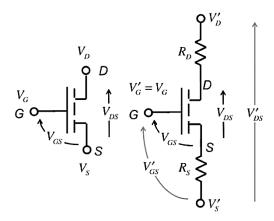

Ток в n-MOSFET (рис. 1) даётся общим выражением

$$I_{DS} = W | Q(x) | \langle v \rangle, \qquad (1)$$

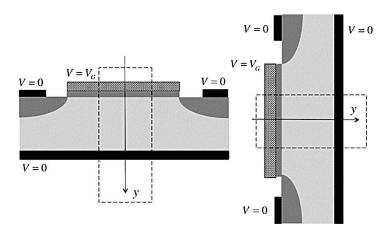

в котором Q есть подвижный поверхностный электронный заряд ( $\mathbb{K}/\mathbb{M}^2$ ) инверсионного слоя в плоскости x-y вглубь подложки p-Si,  $\langle v \rangle$  — средняя скорость электронов в инверсионном слое; W — ширина слоя. Предполагается, что транзистор однороден вдоль оси z, направленной за рисунок, а электроны движутся вдоль оси x от истока x стоку (направление тока  $I_{DS}$  противоположное).

Заряд Q называют зарядом инверсионного слоя, поскольку речь идёт об электронном заряде в полупроводнике p-типа. Заряд и скорость изменяются при движении вдоль канала, а ток постоянен, если только предполагать, что процессы рекомбинации-генерации электронов в канале не происходят. Поэтому величину тока можно вычислять в любой точке канала, где это удобно.

Пусть  $V_S=V_D=0$ , а  $V_{GS}>0$ . Транзистор находится в равновесном состоянии, тока нет. В этом случае заряд Q распределён равномерно вдоль канала, и он небольшой, если  $V_{GS}< V_T$ . При

**Рис. 1.** Упрощённое изображение n-Si MOSFET в режиме обогащения. Ось y направлена вглубь подложки, а ось z — вдоль ширины канала проводимости с инверсионным зарядом, поскольку  $V_{GS} > V_T$ . Показано равномерное ( $V_S = V_D = 0$ ) распределение электронного заряда в пределах канала проводимости, соединяющего n-допированные терминалы S и D, от начала канала в точке x = 0 до x = L.

$V_{GS} > V_{T}$  отрицательный заряд пропорционален их разности, а именно:

$$Q(V_{GS}) = -C_{ox}(V_{GS} - V_T), \qquad (2)$$

$$C_{ox} = \kappa_{ox} \varepsilon_0 / t_{ox} \,, \tag{3}$$

где  $C_{ox}$  есть поверхностная ёмкость диэлектрической прокладки  $(\Phi/\text{m}^2)$ , обратно пропорциональная её толщине  $t_{ox}$ . При  $V_{GS} \leq V_T$  заряд предполагается пренебрежимо малым.

Когда  $V_D > V_S$  зарядовая плотность в инверсионном слое изменяется по ходу вдоль канала проводимости, как и скорость электронов. Как мы увидим позже при более детальном обсуждении электростатики MOS, в «хорошем» транзисторе зарядовая плотность Q в самом начале канала (x=0) даётся именно выражением (2). С целью вычислить  $\underline{I_{DS}}\Big|_{x=0}$ , где мы уже знаем заряд Q согласно (2), потребу-

ется вычислить среднюю скорость  $\langle \underline{v}|_{x=0} \rangle$  в начале канала.

**Линейная область.** При небольших напряжениях на стоке  $V_{DS}$  наблюдается линейный участок на выходной характеристике. Выше порога  $V_{T}$  электрическое поле E в канале постоянное, и для средней скорости электронов можно написать

$$\langle v \rangle = -\mu E = -\mu V_{DS}/L,$$

(4)

где  $\mu$  — подвижность электронов, L — длина канала проводимо-

сти, что с учётом (1) и (2) даёт классическое выражение для тока стока MOSFET при небольших напряжениях на стоке, а именно:

$$I_{DS} = \frac{W}{L} \mu C_{ox} \left( V_{GS} - V_T \right) V_{DS}.$$

(5)

В традиционной теории MOSFET под подвижностью подразумевается некая эффективная подвижность  $\mu_{\rm eff}$ , трактуемая как подвижность, усреднённая по глубине инверсионного слоя. Она меньше чем подвижность электронов в массивном образце, что связывают с рассеянием электронов на шероховатостях граничной поверхности раздела  $SiO_2$ —Si.

Уравнение (5) может быть непосредственно использовано для оценки порогового напряжения  $V_T$ . Для напряжений на затворе  $V_{GS}$ , достаточно превышающих  $V_T$ , ток стока  $I_{DS}$  растёт линейно с  $V_{GS}$ . Экстраполяция этой линейной зависимости на  $I_{DS}=0$  позволяет определить так называемое экстраполяционное значение порогового напряжения  $V_T$ . Различные методы определения  $V_T$  можно найти в [8].

Область насыщения: скорость насыщения. При больших  $V_{DS}$  в области насыщения выходных характеристик MOSFET ведёт себя как источник тока, контролируемый напряжением (рис. 7 в [10]). Для относительно небольшого напряжения  $V_{DS}\approx 1$  В электрическое поле в канале проводимости нанотранзистора ( $L\approx 20$  нм) велико — значительно выше  $\approx 10$  кВ/см, необходимых для насыщения скорости в массивном Si. Если электрическое поле велико вдоль всего канала при  $V_{DS}>V_{DSAT}$ , то скорость электронов постоянна и равна  $v_{sat}$ , и среднюю скорость можно записать в виде

$$\langle v(x) \rangle = v_{sat} \approx 10^7 \text{ cm/c.}$$

(6)

Подставляя (6) и (2) в (1), получаем классическое выражение для тока стока MOSFET, насыщенного по скорости, а именно:

$$I_{DS} = W C_{ox} v_{sat} \left( V_{GS} - V_T \right). \tag{7}$$

В реальных транзисторах ток не насыщается полностью, а медленно увеличивается с ростом напряжения на стоке.

Наконец, нужно обратить внимание на то, что в нанотранзисторах максимальная скорость в канале проводимости не насыщается даже при очень высоком электрическом поле. В учебниках, излагающих традиционный подход к теории MOSFET, тем не менее, предполагается, что скорость электронов насыщается при высоком электрическом поле в канале проводимости.

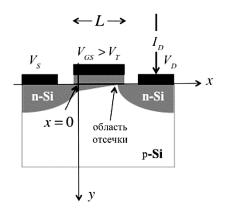

**Область насыщения: классическая область отсечки.** Рассмотрим MOSFET с достаточно протяжённым каналом при высоком напря-

Рис. 2. Длинноканальный MOSFET с указанием на область отсечки. Переменная глубина канала на рисунке иллюстрирует изменение зарядовой плотности вдоль канала – плотность заряда больше в начале истока и уменьшается по мере приближения к стоку. Физическая глубина канала ведёт себя противоположным образом: глубина канала растёт от истока, где потенциал поля затвора наибольший, к стоку, где потенциал поля затвора наименьший. Длина канала, на протяжении которой плотность заряда существенна, есть L' < L.

жении на стоке. В этом случае электрическое поле умеренное и насыщение по скорости не ожидается. Тем не менее, ток стока насыщается, и должна быть какая-то другая причина этого. Явление это наблюдалось ещё на заре науки о полевых транзисторах, когда длина канала составляла около 10 мкм (= 10000 нм) и объяснением насыщения тока стока считалась отсечка вблизи стока.

При высоком напряжении на стоке потенциал в канале существенно меняется от значения  $V_{\scriptscriptstyle S}$  на истоке до значения  $V_{\scriptscriptstyle D}$  на стоке, к более подробному рассмотрению хода которого мы вскоре вернёмся. Перепишем (2) в виде

$$Q(V_{GS}, x) = -C_{ox}[V_{GS} - V_T - V(x)],$$

(8)

где V(x) есть потенциал, изменяющийся вдоль канала проводимости длины L. Согласно (8), если  $V_D=V_{GS}-V_T$  на стоке ( x=L ), заряд на стоке  $Q(V_{GS},L)=0$ : говорят об отсечке канала на стоке. Согласно (1), если заряд Q=0, то ток стока должен обнуляться; на самом же деле наблюдается значительный ток стока. Это связано с тем, что в области отсечки канала электроны в сильном электрическом поле движутся очень быстро, так что плотность заряда конечна, хотя и очень небольшая. Ток насыщается при напряжении на стоке выше  $V_{GS}-V_T$ , поскольку в этой области добавляется ещё потенциал отсечки. Рассмотрим ситуацию более подробно.

Итак, мы имеем достаточно протяжённый канал MOSFET при

высоком напряжении на затворе и при напряжении на стоке, большем  $V_{GS}-V_{T}$ . Практически вдоль всего канала имеется инверсионный слой, и  $\upsilon(x)=-\mu E(x)$ . Когда электроны заходят в область отсечки, сильное электрическое поле быстро переносит их к стоку (рис. 21 в [10]).

Для той части инверсионного канала, для которой плотность заряда велика, среднюю скорость можно записать в виде

$$\langle v(x) \rangle = -\mu E(x)$$

. (9)

Напряжение в начале канала  $V(\mathbf{0}) = V_S = \mathbf{0}$ , а напряжение в конце канала в области отсечки есть  $V_{GS} - V_T$ . Электрическое поле в начале канала, как будет показано ниже,

$$E(0) = \frac{V_{GS} - V_T}{2L'}, (10)$$

где множитель двойка требуется для корректного учёта нелинейности электрического поля в канале, в чем мы убедимся позже, а L' есть длина канала проводимости, не затронутого отсечкой. Подстановка (10) в (9) для начала канала даёт

$$\langle v(0) \rangle = -\mu E(0) = -\mu \frac{V_{GS} - V_T}{2L'}.$$

(11)

Подставляя, наконец, (2) и (11) в (1), получаем так называемый квадратичный закон для выходной характеристики достаточно длинного канала MOSFET:

$$I_{DS} = \frac{W}{2L'} \mu C_{ox} \left( V_{GS} - V_T \right)^2.$$

(12)

В реальных условиях ток не насыщается полностью, а медленно растёт с увеличением напряжения на стоке, в то время как область отсечки медленно сдвигается по направлению к истоку, что эффективно уменьшает длину L' проводящей части канала проводимости. Вычисление цельной ВАХ: от линейной части до квадратичной области насыщения. Уравнения (5) и (12) описывают линейную часть и область насыщения в рамках традиционной теории MOSFET. Покажем, как написать уравнение цельной выходной характеристики с позиций этого же подхода. Начнём с общего уравнения (1) с подстановкой в него уравнения (4) через потенциал электрического поля:

$$I_{DS} = W |Q(x)| \langle v(x) \rangle = W |Q(x)| \mu \frac{dV}{dx}.$$

(13)

После подстановки выражения (8) для заряда получаем:

$$I_{DS} = W \mu C_{ox} [V_{GS} - V_T - V(x)] dV/dx, \qquad (14)$$

разделяем переменные и интегрируем вдоль канала проводимости

$$I_{DS} \int_{0}^{L'} dx = W \mu C_{ox} \int_{V_{S}}^{V_{D}} (V_{GS} - V_{T} - V) dV$$

(15)

в предположении постоянства вдоль канала как подвижности, так и тока стока. После интегрирования окончательно получаем искомое уравнение:

$$I_{DS} = \frac{W}{L'} \mu C_{ox} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right].$$

(16)

Это уравнение даёт ток стока для  $V_{GS}>V_T$  и  $V_{DS}\le \left(V_{GS}-V_T\right)$ . Заряд в (8) зануляется при  $V_{DS}=V_{GS}-V_T$ , обозначая начало области отсечки. Ток за отсечкой находим из (16) при  $V_{DS}=V_{GS}-V_T$ , а именно,

$$I_{DS} = \frac{W}{2L'} \mu C_{ox} \left( V_{GS} - V_T \right)^2, \tag{17}$$

и изменяется этот ток только с ростом  $V_{DS}$ , поскольку эффективная длина канала уменьшается в результате отсечки ( L' < L ).

Уравнения (16) и (17) исчерпывают суть квадратичного закона выходных характеристик MOSFET, не только в линейной области и в области насыщения, а при любых напряжениях.

## 3. ИЗМЕНЕНИЕ ЭЛЕКТРИЧЕСКОГО ПОЛЯ ВДОЛЬ КАНАЛА

Излагая традиционную модель MOSFET, обычно предполагают, что электрическое поле в достаточно длинном канале при низком напряжении на стоке есть  $V_{DS}/L$ , а при высоком напряжении есть  $\left(V_{GS}-V_{T}\right)/2L'$ . Вычислим ход электрического поля в канале и покажем, что эти предположения действительно справедливы.

Из (14) и (16) имеем:

$$\frac{1}{L'} \left[ \left( V_{GS} - V_T \right) V_{DS} - \frac{V_{DS}^2}{2} \right] = \left[ V_{GS} - V_T - V(x) \right] \frac{dV}{dx}; \tag{18}$$

разделяем переменные и после интегрирования от истока при  $x=0,\ V_S=0$  до произвольной точки в канале x с V=V(x) получаем квадратное уравнение для V(x):

$$\left[ \left( V_{GS} - V_T \right) V_{DS} - \frac{V_{DS}^2}{2} \right] \frac{x}{L'} = \left( V_{GS} - V \right)_T V(x) - \frac{V^2(x)}{2} , \qquad (19)$$

решая которое, получаем:

$$V(x) = (V_{GS} - V_T) \left[ 1 - \sqrt{1 - \frac{2(V_{GS} - V_T)V_{DS} - V_{DS}^2/2}{(V_{GS} - V_T)^2}} \left(\frac{x}{L'}\right) \right]. \quad (20)$$

Дифференцируя это уравнение, находим электрическое поле.

Рассмотрим два случая. Для небольших значений напряжения на стоке  $V_{DS}$  , на линейном участке BAX имеем

$$V(x) = (V_{GS} - V_T) \left[ 1 - \sqrt{1 - \frac{2V_{DS}}{(V_{GS} - V_T)} \left(\frac{x}{L'}\right)} \right].$$

(21)

Поскольку для малых аргументов  $\sqrt{1-x} \approx 1-x/2$ , уравнение (21) упрощается до

$$V(x) = V_{DS} \frac{x}{L}, \qquad (22)$$

имея в виду, что при небольших значениях напряжения на стоке L'=L. Дифференцируя (22), получаем ожидаемый результат при малых напряжениях на стоке  $V_{DS}$ :

$$-\frac{dV(x)}{dx} = E = -\frac{V_{DS}}{L}.$$

(23)

Оценим электрическое поле в условиях отсечки канала:  $V_{\scriptscriptstyle DS} = V_{\scriptscriptstyle GS} - V_{\scriptscriptstyle T}$ . Из (20) имеем:

$$V(x) = (V_{GS} - V_T)(1 - \sqrt{1 - x/L'})$$

(24)

и электрическое поле

$$E(x) = -\frac{(V_{GS} - V_T)}{2L'} \left[ \frac{1}{\sqrt{1 - x / L'}} \right].$$

(25)

При x=0 из (25) следует принятый ранее без доказательства результат (10), а при x=L' наступает отсечка, и  $E(L')\to\infty$ . Это ожидаемый результат, поскольку в этой модели заряд обнуляется в области отсечки, так что для поддержки конечного тока требуется бесконечно большое поле.

# 4. НАСЫЩЕНИЕ СКОРОСТИ И НАСЫЩЕНИЕ ТОКА СТОКА

Мы рассматриваем сейчас традиционный подход к теории MOSFET. Уравнения (5), (7) и (12) описывают ход выходной ха-

рактеристики в линейной области и в области насыщения. Были изложены два различных подхода к описанию тока в области насыщения. В одном случае насыщение тока происходило за счёт насыщения скорости электронов в той части канала, где электрическое поле велико. В другом случае причина насыщения была связана с развитием области отсечки канала вблизи стока. Когда среднее электрическое поле в канале намного больше критического поля для насыщения скорости ( $\approx 10 \text{ кB/см}$ ), тогда лучше работает первая модель:

$$\frac{V_{GS} - V_T}{2L} >> E_{cr} \approx 10 \text{ kB/cm.}$$

(26)

Подставляя сюда типичные значения  $V_{GS}=V_{DD}=1$  В и  $V_T=0,2$  В, находим, что модель насыщения скорости приемлема при  $L\leq 1$  мкм. Действительно, подобные модели впервые начали широко применяться в 80-х годах прошлого века, когда длины каналов достигли одного микрометра [11].

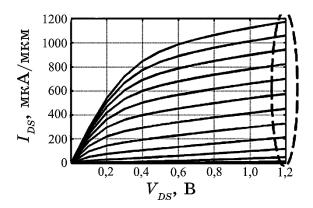

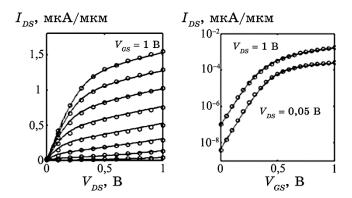

На рисунке 3 показаны выходные характеристики n-Si MOSFET, включённого по схеме с общим истоком, при  $L\approx 60\,$  нм. Очевидно, что при больших  $V_{DS}$  ток  $I_{DS}\propto V_{GS}-V_{T}$ , так что такой транзистор хорошо описывается моделью насыщения скорости (7).

Для транзистора на этом рисунке  $V_T\approx 0,4$  В. Для верхнего графика с максимальным напряжением на затворе модель отсечки даёт  $V_{DSAT}=V_{GS}-V_T=1,2-0,4\approx 0,8$  В, что слишком много и указывает на то, что ток стока не насыщается за счёт классической отсечки. Обсуждение  $V_{DSAT}$  при насыщении скорости можно найти в [8, 9].

**Рис. 3.** Выходные характеристики n-Si MOSFET, включённого по схеме с общим истоком, при  $L\approx 60$  нм. Характеристики показаны с шагом 0,1 В, для верхней кривой  $V_{GS}=1,2\,$  В. Обращает на себя внимание, что при больших  $V_{DS}$  ток растёт линейно с ростом напряжения на затворе. Это признак того, что в канале имеет место насыщение скорости [12].

Хотя и кажется, что модели насыщения скорости удовлетворительно описывают короткоканальные MOSFET, но есть нечто настораживающее. Тщательное компьютерное моделирование транспорта электронов в наноразмерных MOSFET неопровержимо показывает, что скорость не насыщается в той части канала нанотранзистора, которая находится под воздействием высокого электрического поля. Просто электронам не хватает времени эффективно рассеяться, чтобы их скорость «насытилась». Электроны проскакивают канал и уходят в сток слишком быстро. И всё же графики на рис. З показывают, что скорость таки насыщается. Это «мистическое» противоречие найдёт своё объяснение, когда мы перейдём к последовательному изложению теории нанотранзисторов.

#### 5. МЕТРИКА НАНОТРАНЗИСТОРОВ

Уравнения (5) и (7) приемлемы для описания выходных характеристик современных короткоканальных транзисторов и могут быть использованы для оценки их метрических показателей [10], а именно:

$$I_{\text{ON}} = W C_{ox} v_{sat} (V_{DD} - V_{T}), V_{T} = V_{T0} - \delta V_{DS},$$

$$R_{\text{ON}} = \left(\frac{\partial I_{DS}}{\partial V_{DS}}\right|_{V_{GS} = V_{DD}, V_{DS} \approx 0}\right)^{-1} = \left(\frac{W}{L} \mu C_{ox} (V_{GS} - V_{T})\right)^{-1},$$

$$g_{m}^{sat} = \frac{\partial I_{DS}}{\partial V_{GS}}\Big|_{V_{GS} = V_{DS} = V_{DD}} = W C_{ox} v_{sat},$$

$$r_{d} = \left(\frac{\partial I_{DS}}{\partial V_{DS}}\right|_{V_{GS} = V_{DD}, V_{DS} > V_{DSAT}}\right)^{-1} = \frac{1}{g_{m}^{sat} \delta}, |A_{v}| = g_{m}^{sat} r_{d} = \delta^{-1}.$$

$$(27)$$

Метрика  $|A_{v}|$  — важный показатель качества в аналоговой электронике.

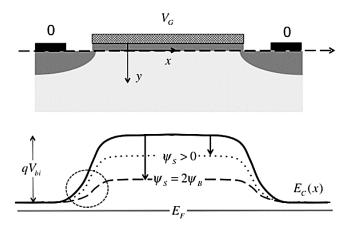

Что же касается зонных диаграмм, то, хотя они не использовались нами в явном виде, они подразумевались в той или иной форме. Начало канала проводимости (x=0) это вершина энергетического барьера на рис. 16 и 17 в [10] или близко к вершине барьера [13]. Как мы увидим позже, в качественном транзисторе заряд на вершине барьера даётся выражением (2). Этот заряд обеспечивается электронами из истока, преодолевшими барьер. Эта локация на вершине барьера, для которой справедливо уравнение (2), известна также как виртуальный исток.

Использование зонных диаграмм особенно полезно для пони-

мания природы отсечки канала. Не сразу понятно, как именно электроны покидают канал проводимости и проходят зону отсечки. Проясняют ситуацию зонные диаграммы. Как видно из рис. 17 в [10], область отсечки — это область сильного электрического поля в районе стока, и наклон  $E_c(x)$  здесь наиболее крутой. Электроны, попавшие в эту область из канала проводимости, просто скатываются и покидают сток. Ничто не может их остановить, если они уже попали в область отсечки.

# 6. НАЧАЛА МОДЕЛИ ВИРТУАЛЬНОГО ИСТОКА

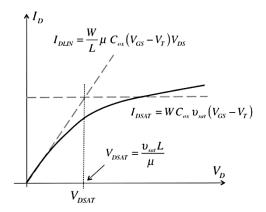

У нас уже есть выражения для тока стока в линейной области (5) и в области насыщения (7), а именно:

$$I_{DLIN} = \frac{W}{L} \mu C_{ox} (V_{GS} - V_{T}) V_{DS}, \ I_{DSAT} = W C_{ox} v_{sat} (V_{GS} - V_{T}), \ \ (28)$$

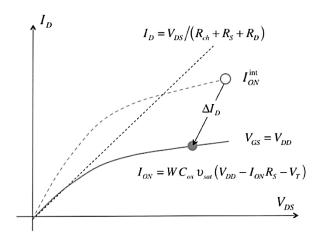

при этом имеется в виду, что  $V_{GS}>V_T$ , так что уравнения (28) не пригодны для подпороговой области ВАХ. Эти уравнения приближённо описывают поведение  $I_{DS} \propto V_{DS}$  (рис. 4); рекомендуется учесть DIBL, как в (18) в [10]. Уравнивание выражений (28),  $I_{DLIN}=I_{DSAT}$ , позволяет ввести понятие напряжения насыщения на стоке как

$$V_{DSAT} = \frac{v_{sat}L}{\mu}.$$

(29)

При  $V_{DS} << V_{DSAT}$  ток  $I_{DS} = I_{DLIN}$  , а при  $V_{DS} >> V_{DSAT}$  ток  $I_{DS} = I_{DSAT}$  .

**Рис. 4.** Выходная характеристика n-MOSFET, включённого по схеме с общим истоком, при некотором значении напряжения на затворе. Пунктирные линии дают ток в линейной области и в области насыщения согласно (28).

Традиционный подход к теории MOSFET позволяет получить выражение для зависимости  $I_{DS} \propto V_{DS}$ , плавно переходящей от линейного участка к области насыщения по мере роста  $V_{DS}$  от нуля до  $V_{DD}$  [8, 9]. Наша задача получить простое полуэмпирическое выражение для всей цельной выходной характеристики  $I_{DS}(V_{DS})$ . Используемый далее подход аналогичен так называемой модели виртуального истока (Virtual Source Model—VS Model) MOSFET, которая нашла успешное применение при моделировании весьма разнообразных нанотранзисторов [14]. Лундстром [15], воспользовавшись изложенным выше традиционным подходом, подошёл несколько иначе к построению модели виртуального истока. По мере совершенствования и развития этой модели в конечном итоге будет построена достаточно простая физическая модель, которая обеспечит точное количественное описание современных нанотранзисторов.

Скорость в канале и напряжение на стоке. Ток стока пропорционален произведению заряда в начале канала и средней скорости электронов там же, а именно:

$$I_{DS}/W = |\underline{Q}|_{x=0} | \times \underline{v}|_{x=0}$$

(30)

Уравнение (28) для линейного тока можно переписать в следующем виде:

$$I_{DLIN}/W = |Q(V_{GS})| v(V_{DS}), Q(V_{GS}) = -C_{ox}(V_{GS} - V_{T}),$$

$$v(V_{DS}) = \left(\mu \frac{V_{DS}}{L}\right). \tag{31}$$

Аналогичным образом перепишем (28) для области насыщения:

$$I_{DSAT}/W = \left|Q\left(V_{GS}\right)\right|\upsilon\left(V_{DS}\right), \ Q\left(V_{GS}\right) = -C_{ox}\left(V_{GS}-V_{T}\right), \ \upsilon\left(V_{DS}\right) = \upsilon_{sat}. \tag{32}$$

Если найти способ аппроксимировать плавный переход средней скорости от своего значения при низком  $V_{DS}$  до значения  $v_{sat}$  при высоком  $V_{DS}$ , то можно получить модель, которая покроет весь интервал значений напряжения на стоке.

В оригинальной модели виртуального истока используется эмпирический подход, согласно которому средняя скорость в начале канала записывается следующим образом [14]:

$$v\left(V_{DS}\right) = F_{SAT}\left(V_{DS}\right)v_{sat}, \quad F_{SAT}\left(V_{DS}\right) = \frac{V_{DS}/V_{DSAT}}{\left[1 + \left(V_{DS}/V_{DSAT}\right)^{\beta}\right]^{1/\beta}}, \quad (33)$$

где  $V_{\scriptscriptstyle DSAT}$  определяется уравнением (29), а эмпирический подгоночный параметр  $\beta$  позволяет вписаться в экспериментально из-

меренную выходную характеристику.

Выбор выражения для функции насыщения тока стока  $F_{SAT}$  был продиктован наблюдением того, что наименьшая из двух скоростей (31) и (32) и есть та скорость, которая ограничивает ток. Это даёт основание написать, что

$$\frac{1}{v(V_{DS})} = \frac{1}{\mu V_{DS}/L} + \frac{1}{v_{sat}}$$

(34)

или иначе

$$v(V_{DS}) = \frac{V_{DS}/V_{DSAT}}{1 + (V_{DS}/V_{DSAT})} v_{sat}.$$

(35)

Уравнение (35) аналогично уравнению (33) за исключением эмпирического параметра  $\beta$ . Типичные значения  $\beta$  для n- и p-Si MOSFET лежат в интервале 1,4–1,8 [14].

Уравнения (2), (30) и (33) описывают линейный ход и область насыщения BAX MOSFET выше порогового значения напряжения для любого напряжения на стоке.

Итак, простую начальную модель MOSFET, пригодную выше порогового напряжения, можно суммировать в виде следующей сводки формул:

$$\begin{split} I_{DS}/W &= \left| Q\left(0\right) \right| \upsilon(0), \\ Q\left(V_{GS}\right) &= 0, \ V_{GS} \leq V_{T}, \\ Q\left(V_{GS}\right) &= -C_{ox}\left(V_{GS} - V_{T}\right), \ V_{GS} > V_{T}, \\ V_{T} &= V_{T0} - \delta V_{DS}, \\ \left\langle \upsilon\left(V_{DS}\right) \right\rangle &= F_{SAT}\left(V_{DS}\right)\upsilon_{sat}, \\ F_{SAT}\left(V_{DS}\right) &= \frac{V_{DS}/V_{DSAT}}{\left[1 + \left(V_{DS}/V_{DSAT}\right)^{\beta}\right]^{1/\beta}}, \ V_{DSAT} &= \frac{\upsilon_{sat}L}{\mu}. \end{split} \tag{36}$$

Эту простую модель MOSFET Лундстром называет моделью виртуального истока нулевого уровня [15]. Она позволяет вычислять весьма правдоподобные выходные характеристики MOSFET. Её дальнейшее развитие и совершенствование с привлечением модели баллистического транспорта Ландауэра приведёт нас к всё более и более количественно точной модели полевого нанотранзистора.

В модели виртуального истока нулевого уровня есть только шесть параметров:

$$C_{ox}$$

,  $V_{T}$ ,  $\mu$ ,  $v_{out}$ ,  $L$ ,  $\beta$ . (37)

Эта модель не пригодна для описания подпороговой области ВАХ. Физически более корректное обсуждение электростатики МОS позволит нам позже количественно учесть и подпороговую область. Но уже на этом уровне модели виртуального истока можно корректно учесть реальные сопротивления терминалов S и D полевого транзистора.

## 7. УЧЁТ ТЕРМИНАЛЬНЫХ СОПРОТИВЛЕНИЙ

На рисунке 5 слева показан идеализированный MOSFET. На практике терминалы S и D полевого транзистора всегда характеризуются своими сопротивлениями. Они влияют на напряжения, подаваемые на транзистор, и сказываются на его характеристиках. Покажем, как можно учесть это влияние.

На рисунке 5 справа показаны принятые обозначения. Напряжениям  $V_D$ ,  $V_S$ ,  $V_G$  идеализированного транзистора соответствуют реальные напряжения  $V_D'$ ,  $V_S'$ ,  $V_G'$ . Сопротивление терминала затвора не учитывается, поскольку речь идёт о режиме постоянного тока: ток затвора нулевой, так что сопротивление затвора не играет роли. Сопротивление затвора играет важную роль в радиочастотных транзисторах, которые нами не рассматриваются.

Связь между идеализированными, внутренними напряжениями (нештрихованными) и внешними напряжениями (штрихованными) даётся простыми выражениями:

$$V_D = V_D' - I_{DS}(V_D, V_S, V_G)R_D, V_S = V_S' + I_{DS}(V_D, V_S, V_G)R_S, V_G = V_G'.$$

(38)

**Рис. 5.** Учёт сопротивлений терминалов S и D MOSFET. Слева: идеализированный MOSFET. Справа: реальный MOSFET, демонстрирующий влияние сопротивлений контактов S и D на напряжения в идеализированном полевом транзисторе.  $^5$

Пусть выходная характеристика идеализированного транзистора  $I_{DS}\left(V_D,V_S,V_G\right)$  известна. Задавшись измеренными сопротивлениями  $R_S$  и  $R_D$  и экспериментальными значениями напряжений  $V_D',V_S',V_G$ , решение системы уравнений (38) позволяет вычислить внутренние напряжения  $V_D$  и  $V_S$  и определить характеристику  $I_{DS}\left(V_D',V_S',V_G\right)$ . Рисунок 6 иллюстрирует влияние учёта сопротивлений кон-

Рисунок 6 иллюстрирует влияние учёта сопротивлений контактов S и D на входную характеристику. Согласно (31), ток в линейной области без учёта сопротивлений  $R_{\scriptscriptstyle S}$  и  $R_{\scriptscriptstyle D}$  даётся выражением

$$I_{DLIN} = \frac{W}{L} \mu C_{ox} (V_{GS} - V_T) V_{DS} = V_{DS} / R_{ch}, \qquad (39)$$

а с учётом сопротивлений контактов —

$$I_{DLIN} = V_{DS}/R_{tot}, (40)$$

где

$$R_{tot} = R_{ch} + R_{S} + R_{D} = R_{ch} + R_{DS}$$

(41)

Таким образом, влияние учёта сопротивлений контактов сводится просто к уменьшению наклона линейного участка входной характеристики (рис. 6).

Как видим, уменьшается также предельный ток насыщения. В идеальном транзисторе сопротивление  $R_{\scriptscriptstyle D}$  не влияет на ту часть

**Рис. 6.** Влияние учёта сопротивлений контактов S и D на BAX MOSFET. Пунктиром показана входная характеристика без учёта сопротивлений контактов. Учёт сопротивлений  $R_S$  и  $R_D$  увеличивает сопротивление канала проводимости и понижает ток  $I_{\rm ON}$ .

области насыщения ВАХ, для которой  $V_{DS} > V_{DSAT}$  (рис. 4), а вот сопротивление  $R_{S}$  уменьшает напряжение на затворе  $V_{GS}$  на величину  $I_{DSAT}R_{S}$ , так что вместо (28) имеем:

$$I_{DSAT} = W C_{ox} v_{sat} \left( V_{GS}' - I_{DSAT} R_{S} - V_{T} \right). \tag{42}$$

Максимальное значение напряжения  $V_{\rm DS}$  есть напряжение питания транзистора  $V_{\rm DD}$ . Влияние сопротивления контактов незначительно, если  $I_{\rm DSAT}R_{\rm S} << V_{\rm DD}$ . Высокая эффективность транзистора обеспечивается значением

$$R_{\rm S} \ll \frac{V_{\rm DD}}{I_{\rm DSAT}}.$$

(43)

Нынешние Si-MOSFET обеспечивают ток  $I_{\rm ON}=1$  мА/мкм при  $V_{\rm DD}=1$  В. Соответственно этому, сопротивление  $R_{\rm S}$  должно быть намного меньше 1000 Ом·мкм, скажем, равно 100 Ом·мкм. Хотя нас, прежде всего, интересует физика идеализированного MOSFET, нужно, однако, при анализе экспериментальных данных помнить о роли сопротивлений контактов. По мере того как канал проводимости в транзисторах уменьшается, поддерживать учёт сопротивлений контактов на должном уровне становится всё сложнее и сложнее.

Воспользуемся уравнением (42) и оценим скорость насыщения  $v_{sat}$  тока  $I_{\rm ON}$  путём анализа входной характеристики MOSFET с  $L\approx 60$  нм на рис. 3. Полученное таким образом значение  $v_{sat}$  как подгоночного эмпирического параметра сравним с известными данными для массивного кремния. Исходные параметры входной характеристики (рис. 3) следующие:

$$I_{\rm ON}=1180$$

мкА /мкм,  $C_{ox}=1,55\cdot 10^{-6}$  Ф /см²,  $R_{DS}=220$  Ом,  $V_{T}=0,25$  В,  $V_{DD}=1,2$  В,  $W=1$  мкм.

Из (42) для  $v_{sat}$  имеем:

$$v_{sat} = \frac{I_{DSAT}}{W C_{ox} (V_{GS} - V_T)} \equiv v_{inj}, \ V_{GS} = V_{DD} - I_{DSAT} R_{SD} / 2.$$

(44)

Для приведённых выше исходных данных получаем:

$$v_{sat} = 0.92 \cdot 10^7 \text{ cm/c.}$$

Любопытно, что полученное значение скорости насыщения тока в нанотранзисторе практически совпадает с данными для массивного образца кремния ( $1\cdot 10^7$  см/с), однако, физика насыщения тока в нанотранзисторах весьма отличается от таковой в массивном кремнии. По этой причине, а вернёмся мы к этому вопросу позже, пере-

**Рис. 7.** Измеренные и рассчитанные по модели VS BAX 32 нм n-MOSFET. Слева: выходные характеристики MOSFET, включённого по схеме с общим истоком, с шагом  $\Delta V_{GS}=0.1$  В. Справа: передаточные характеристики. Использовалась модель VS более высокого уровня [14], одинаково пригодная как для подпороговых, так и для надпороговых напряжений и подробно излагаемая далее.  $^7$

именуем скорость насыщения  $v_{sat}$  на скорость впрыска (injection velocity)  $v_{ini}$  .

Казалось бы, можно ожидать, что традиционная модель MOSFET применима только для транзисторов с достаточно длинными каналами проводимости, поскольку она основана на таких предположениях как диффузионный транспорт в омической области ВАХ и насыщение скорости в высоких полях. Удивительно, но оказывается, эта модель достаточно аккуратно описывает входные характеристики MOSFET с длиной канала меньшей 100 нм, как это видно из рис. 7.

Для достижения такого согласия с экспериментальными данными оказалось достаточным два физических параметра в модели VS, считая их эмпирическими параметрами, несколько модифицировать их таким образом, чтобы модель стала пригодной для большей части транзисторов. Эти два подгоночных параметра — скорость впрыска  $v_{inj}$  (скорость насыщения  $v_{sat}$  в традиционной модели) и кажущаяся подвижность  $\mu_{app}$  (просто подвижность  $\mu$ в традиционной модели). То обстоятельство, что простая традиционная модель МОSFET вполне удовлетворительно описывает даже современные транзисторы, говорит, скорее всего, о том, что эта модель на самом деле учитывает нечто существенное из физики нанотранзисторов, к более глубокому изучению которой мы перейдём позже.

# 8. ПРИБЛИЖЕНИЕ ИСТОЩЕНИЯ И УРАВНЕНИЕ ПУАССОНА

До сих пор мы обсуждали основные концепции базовой модели MOSFET. Предполагая, что инверсионный заряд в самом начале

канала проводимости даётся выражениями

$$\begin{split} Q\left(V_{GS}\right) &= 0, \ V_{GS} \leq V_{T}, \\ Q\left(V_{GS}\right) &= -C_{G}\left(V_{GS} - V_{T}\right), \ V_{GS} > V_{T}, \\ V_{T} &= V_{T0} - \delta V_{DS}, \end{split} \tag{45}$$

с использованием простых традиционных моделей для средней скорости электронов в начале канала были получены уравнения для моделирования входных характеристик MOSFET. Зададим себе следующие важные вопросы. Почему заряд Q растёт линейно с напряжением на затворе при  $V_{GS} > V_T$ ? Что такое ёмкость затвора  $C_G$  (она несколько меньше  $C_{ox}$ )? Как небольшой заряд при  $V_{GS} < V_T$  изменяется с напряжением на затворе? Ответы на эти вопросы мы получим, рассматривая 1D-электростатику MOS. Кроме того, возникают вопросы по физике DIBL: что именно определяет значение параметра  $\delta$ ? Для ответа на этот вопрос нам нужно будет обратиться уже к 2D-электростатике MOS. Понимание 1D- и 2D-электростатики MOS абсолютно необходимо для построения теории полевых транзисторов, поскольку именно электростатика определяет, как именно напряжения на терминалах транзистора влияют на барьер канала проводимости [6,7].

Энергия и изгиб зон. Мы хотим понять, каким образом терминальные напряжения и собственно даже дизайн MOSFET влияют на электростатический потенциал  $\psi(x,y,z)$ . Направления осей системы координат выберем следующим образом: ось x направлена от истока к стоку, ось y — вглубь полупроводниковой под-

**Рис. 8.** Выбор направления оси y вглубь полупроводниковой подложки (слева) и ориентация канала проводимости (снизу-вверх) при изображении зонных диаграмм (справа).<sup>8</sup>

ложки, ось z — вдоль ширины канала проводимости (рис. 8). Потребуется искать решение уравнения Пуассона:

$$\nabla \cdot \mathbf{D}(x, y, z) = \rho(x, y, z)$$

или  $\nabla^2 \psi(x, y, z) = -\frac{\rho(x, y, z)}{\varepsilon_s}$ , (46)

где  ${\bf D}$  — вектор смещения,  $\rho$  — зарядовая плотность,  $\epsilon_{\rm S}$  — диэлектрическая проницаемость полупроводника, который предполагается пространственно однородным.

В общем случае нужно искать пространственное решение, однако, обычно предполагается, что канал проводимости однороден по ширине (вдоль ось z), так что достаточно 2D-решения. Мы начнём обсуждение с 1D-электростатики — в направлении, перпендикулярном каналу вглубь полупроводниковой подложки. Итак, имеем достаточно длинный канал и рассмотрим поведение  $\psi(y) \propto y$  в середине канала, где влияние потенциалов со стороны истока и стока минимально, так что 2D-эффектами (вдоль оси x) можно пренебречь.

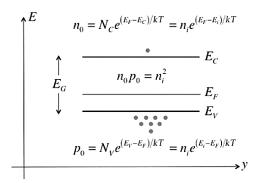

Удобным количественным решением уравнения Пуассона служат диаграммы зонной энергии. Рассмотрим влияние напряжения на затворе на зависимость E(y) вглубь канала проводимости в полупроводниковой подложке. Рисунок 9 иллюстрирует ситуацию, когда зоны плоские, т.е. потенциал нулевой (или постоянный в направлении y) и зонная энергия не зависит от координаты (глубины y).

Плотности электронов  $n_0$  и плотности дырок  $p_0$  зависят экспоненциально от разности между границами зон и энергией Ферми в предположении, что носители тока подчиняются статистике Больцмана. Предэкспоненты

$$N_C \equiv 2 \left[ \frac{2\pi m_n kT}{h^2} \right]^{3/2}, \ N_V \equiv 2 \left[ \frac{2\pi m_p kT}{h^2} \right]^{3/2}$$

(47)

**Рис. 9.** При постоянном электростатическом потенциале зоны плоские. Показана ширина запрещённой зоны  $E_G$ .

носят названия: эффективные плотности состояний электронов в зоне проводимости и эффективные плотности состояний дырок в валентной зоне соответственно. Уравнения для плотностей электронов  $n_0$  и дырок  $p_0$  легко запомнить, если понять, почему  $N_C$  и  $N_V$  называют эффективной плотностью состояний. Это как если бы все уровни энергии, например, в зоне проводимости эффективно совместить с энергией дна зоны проводимости  $E_C$  поместив туда все  $N_C$  электронов. В результате концентрация электронов  $n_0$  есть просто произведение  $N_C$  и вероятности того, что состояние с энергией  $E_C$  занято.

Значения  $N_C$  и  $N_V$  колеблются около  $10^{19}\,\mathrm{cm}^{-3}$ , отличаясь только за счёт различия в эффективных массах электронов  $m_n$  и дырок  $m_p$ . Различны они и для разных полупроводников (табл.).

Концентрации мажоритарных носителей тока даются выражениями

$$n_0 = N_D - N_A, \quad p_0 = N_A - N_D,$$

(48)

где  $N_{\scriptscriptstyle D}$  и  $N_{\scriptscriptstyle A}$  — концентрации доноров и акцепторов, предполагая обычно их полную ионизацию. Концентрации миноритарных носителей тока находятся из

$$n_0 p_0 = n_i^2 \,, \tag{49}$$

где  $n_i$  есть концентрация собственных носителей, составляющая для Si около  $10^{10}~{\rm cm}^{-3}$  при  $300~{\rm K}$  и зависящая от  $E_G$  и T.

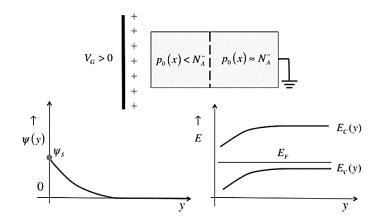

Рисунок 10 показывает, как влияет положительный потенциал на затворе на ход электростатического потенциала. Потенциал  $\psi_S$  на поверхности полупроводника будет положительным:  $0<\psi_S< V_{GS}$ . Если подложка полупроводника заземлена ( $\psi|_{y\to\infty}=0$ ), можно ожидать, что электростатический потенциал экспоненциально ниспадает до нуля.

Положительный электростатический потенциал понижает потенциальную энергию электронов, так что зоны изгибаются с изменением электростатического потенциала согласно

$$E_c(y) = \operatorname{const} - q \, \psi(y) \,. \tag{50}$$

Если электростатический потенциал растёт изнутри подложки по направлению к её поверхности, то энергия зон в том же направлении падает (рис. 10).

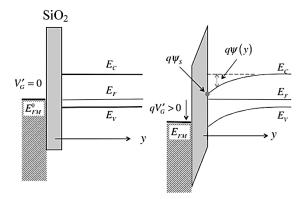

Прежде чем переходить к рассмотрению изгиба зон в зависимости от приложенного напряжения на затворе, определим некоторые понятия (рис. 11). Для начала рассмотрим гипотетический идеальный «металлический» затвор, фермиевский уровень  $E_{FM}^0$  которого

**ТАБЛИЦА.** Значения  $N_c$  и  $N_v$  для Ge, Si и GaAs при 300 К·см $^{-3}$ .  $^{10}$

|            | Ge                                   | Si                   | GaAs                |

|------------|--------------------------------------|----------------------|---------------------|

| $N_c$      | $\textbf{1,04}\cdot\textbf{10}^{19}$ | $2,8 \cdot 10^{19}$  | $4,7 \cdot 10^{17}$ |

| $N_{_{V}}$ | $6,0 \cdot 10^{18}$                  | $1,04 \cdot 10^{19}$ | $7,0\cdot 10^{18}$  |

**Рис. 10.** Влияние положительного напряжения на затворе ( $V_{GS}>0$ ) на ход электростатического потенциала (слева) и изгиб зон (справа).

совпадает с таковым  $E_F$  кремниевой подложки (рис. 11, слева). Эту ситуацию называют условием плоских зон (flat-band (FB) condition) — зоны в кремнии и в его диэлектрическом слое плоские.

Для некоторого гипотетического «металлического» затвора плоские зоны будут при  $V_G'=0$ . Штрихом подчёркивается то обстоятельство, что затвор сделан из некоторого гипотетического вещества. На практике всегда имеет место разность работ выхода  $\Phi_{MS}$  между металлическим электродом затвора и полупроводниковой подложкой. Условие плоских зон не выполняется при  $V_G=0$  в отличие от напряжения  $V_G=V_{FB}=\Phi_{MS}/q$  такого, которое нивелирует разность работ выхода.

Напомним, что при подаче напряжения на контакт его уровень Ферми понижается. Как показано на рис. 11, фермиевский уровень электрода затвора понижается от значения  $E_{FM}^0$  при  $V_G'=0$  до значения  $E_{FM}=E_{FM}^0-qV_G'$ . Положительный потенциал, поданный на затвор, понижает электростатический потенциал в окиси кремния и в полупроводниковой подложке как это следует из решений уравнений Лапласа и Пуассона, к рассмотрению которых мы приступим ниже. Если за нуль отсчёта электростатического потенциала принять его значение в массивной подложке,  $\psi|_{y\to\infty}=0$ , то электростатический потенциал на глубине y от поверхности подложки даётся выражением

**Рис. 11.** Слева: выполнение условия плоских зон в идеализированной структуре MOS. Справа: изгиб зон в результате подачи положительного напряжения на затвор.  $^{12}$

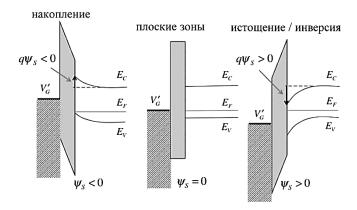

**Рис. 12.** Характер изгиба зон при трёх различных напряжениях на затворе: накопление носителей (слева  $V_{GS}<0$ ), истощение/инверсия (справа  $V_{GS}>0$ ), плоские зоны (по центру  $V_{GS}=0$ ).

$$\psi(y) = \frac{E_C(\infty) - E_C(y)}{q}.$$

(51)

Обращает на себя внимание (рис. 11, справа), что уровень Ферми в полупроводнике плоский, даже если приложено напряжение на затворе. Связано это с тем, что диэлектрическая прокладка не даёт току затвора пройти в подложку, так что металлический контакт затвора и полупроводниковая подложка порознь находятся в равновесии с различными фермиевскими уровнями (рис. 11, справа).

Теперь мы готовы обсудить изгиб зон при подаче на затвор напряжения разных знаков (рис. 12). Если подаётся отрицательное напряжение на затвор, в диэлектрическом слое и в полупро-

воднике индуцируется отрицательный электростатический потенциал и зоны изгибаются вверх, поверхностный потенциал отрицательный:  $\psi|_{y=0} = \psi_S < 0$ . Концентрация дырок увеличивается вблизи границы раздела диэлектрик-полупроводник, поскольку валентная зона изгибается вверх навстречу уровню Ферми. Суммарный заряд вблизи поверхности полупроводника положительный. Этот накопленный заряд (accumulation charge) локализуется очень близко к поверхности подложки и иногда даже аппроксимируется  $\delta$ -функцией.

При подаче положительного напряжения на затвор в диэлектрическом слое и в полупроводнике индуцируется положительный электростатический потенциал и зоны изгибаются вниз, поверхностный потенциал положительный:  $\psi|_{y=0} = \psi_S > 0$ . Поскольку валентная зона изгибается вниз от уровня Ферми (рис. 12, справа), концентрация дырок уменьшается. Легко запомнить в качестве мнемонического правила: положительный потенциал затвора отталкивает положительно заряженные дырки от поверхности раздела диэлектрик-подложка. Нужно только помнить, что «дырки» — это искусственное, а не физическое понятие, вместе с тем чрезвычайно удобное и ток в валентной зоне это поток электронов (как и в зоне проводимости), а не умозрительных «дырок». Результатом подачи положительного напряжения на затвор является появление слоя истощения (depletion layer), слоя толщиной  $W_{\scriptscriptstyle D}$ , в котором концентрация дырок пренебрежимо мала,  $p_0 << N_A^-$  (рис. 10). Если изгиб зон не слишком велик, то концентрация электронов также невелика. В противном случае, при значительном изгибе зон электроны начинают накапливаться вблизи поверхности раздела, образуя инверсионный слой (inversion layer), связывающий n-допированные области контактов S и D и ответственный за возникновение тока в MOSFET. Явление инверсии подробно обсудим позже.

Наконец, нужно помнить, что зонные диаграммы на рис. 12 относятся к подложке из *p*-Si. Эти диаграммы легко перерисовать для подложки *n*-типа. Термины «накопление» и «истощение» всегда указывают на накопление и истощение основных носителей тока, а термин «инверсия» всегда относится к миноритарным носителям тока. Нужно только помнить, что отнесение носителей тока к основным или миноритарным является искусственным и условным, однако, весьма удобным, поскольку электрический ток — это всегда поток электронов.

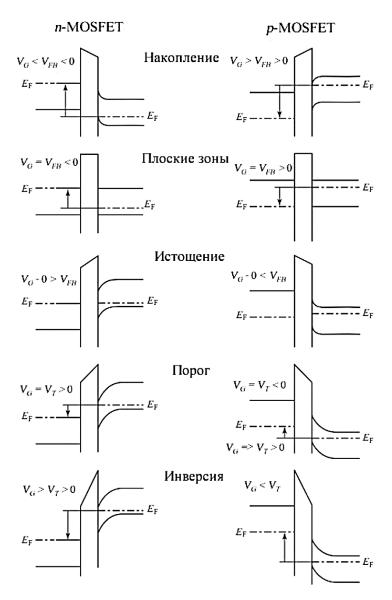

Забегая несколько вперёд, приведём сводную таблицу (рис. 13) трёх режимов — накопления, истощения и инверсии, а также двух переходных локаций — плоских зон и порога.

**Уравнение Пуассона**—**Больцмана.** Наша задача состоит в том, чтобы понять, как заряд в полупроводнике

**Рис. 13.** Характер изгиба зон в режимах накопления, истощения и инверсии, а также в двух переходных локациях — плоских зон и порога. Отрицательному напряжению на затворе соответствуют стрелки «вверх», а положительному — стрелки «вниз» [16].  $^{14}$

$$Q_{S} = \int_{0}^{\infty} \rho(y) dy = q \int_{0}^{\infty} (p_{0}(y) - n_{0}(y) + N_{D}^{+} - N_{A}^{-}) dy \ [\text{K/m}^{2}]$$

(52)

зависит от электростатического потенциала у. Нижний индекс «0»

означает, что полупроводниковая подложка находится в равновесии. Нас также интересует заряд, обязанный подвижным электронам,

$$Q = -q \int_{0}^{\infty} n_0(y) \, dy \, \left[ \mathbb{K} / \mathbb{M}^2 \right], \tag{53}$$

поскольку именно электроны являются носителями тока в MOSFET.

Количественным решением для потенциала и заряда в полупроводнике служат диаграммы зонной структуры. Для нахождения хода потенциала в полупроводнике нужно решать уравнение Пуассона. Запишем это уравнение для 1D-полупроводника:

$$\frac{d^2 \Psi}{dy^2} = \frac{-q}{\varepsilon_S} \left( p_0(y) - n_0(y) + N_D^+ - N_A^- \right). \tag{54}$$

Имеется в виду полупроводник p-типа, для которого  $N_D=0$ . Подразумевается полная ионизация допантов:  $N_A^-=N_A$ . Подложка (B) не заряжена,  $p_B-n_B-N_A=0$ , так что  $N_A=p_B-n_B$ , и уравнение Пуассона теперь —

$$\frac{d^2\Psi}{dy^2} = \frac{-q}{\varepsilon_S} \left( p_0(y) - n_0(y) + n_B - p_B \right), \tag{55}$$

где

$$p_{\scriptscriptstyle R} \cong N_{\scriptscriptstyle A}, \ n_{\scriptscriptstyle R} \cong n_{\scriptscriptstyle i}^2/N_{\scriptscriptstyle A}. \tag{56}$$

Индексом «B» подчёркивается, что речь идёт о равновесных концентрациях в подложке. Учитывая (56), переписываем (55) в виде

$$\frac{d^2 \Psi}{dy^2} = \frac{-q}{\varepsilon_S} \left( p_0(y) - N_A - n_0(y) + n_i^2 / N_A \right). \tag{57}$$

В этом уравнении три неизвестных:  $\psi(y)$ ,  $n_0(y)$  и  $p_0(y)$ . Нужны ещё два уравнения.

Вспомним, что MOSFET находится в равновесии при любом напряжении на затворе, поскольку диэлектрическая прокладка в идеале не пропускает ток. А в равновесии плотности носителей тока зависят от положения уровня Ферми (константа в равновесном состоянии) и от границ зон. Поэтому можно записать, что

$$n_0(y) = n_B e^{+q\psi(y)/kT} = \frac{n_i^2}{N_A} e^{+q\psi(y)/kT}, \ p_0(y) = p_B e^{-q\psi(y)/kT} = N_A e^{-q\psi(y)/kT}, (58)$$

и окончательно уравнение (57) принимает вид:

$$\frac{d^2 \Psi}{dy^2} = \frac{-q}{\varepsilon_S} \left[ N_A \left( e^{-q \Psi(y)/kT} - 1 \right) - \frac{n_i^2}{N_A} \left( e^{+q \Psi(y)/kT} - 1 \right) \right]. \tag{59}$$

Это уравнение известно как уравнение Пуассона—Больцмана. В нашем случае оно описывает 1D-полупроводник p-типа в равновесии, с полностью ионизированными допантами. Осталось записать граничные условия. Имея в виду полубесконечный полупроводник, имеем:

$$\underline{\Psi}|_{y=0} = \Psi_S, \ \underline{\Psi}|_{y\to\infty} = 0.$$

(60)

На практике значение  $\psi_S$  обычно выбирают в соответствии с потенциалом затвора.

С методами решения нелинейного дифференциального уравнения Пуассона—Больцмана можно подробно познакомиться в [8, 9, 17]. Можно получить его приближенные решения, если полупроводниковая подложка MOSFET находится в режиме накопления или истощения или сильной инверсии. Начнём мы с режима истощения.

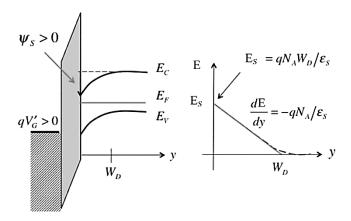

Приближение истощения. Весьма достоверное приближенное решение для электростатического потенциала и электрического поля можно получить, если транзистор находится в режиме истощения. В этом режиме зоны изгибаются вниз и концентрация дырок пренебрежимо мала на глубине  $y \leq W_D$ . В режиме истощения дно зоны проводимости расположено всё ещё достаточно высоко относительно уровня Ферми (это не так в режиме инверсии), и концентрация электронов, как и дырок, мала. В итоге, зарядовая плотность

$$\rho(y) = q \left( p_0(y) - n_0(y) + N_D^+ - N_A^- \right)$$

(61)

существенно упрощается. Пренебрегая незначительной концентрацией носителей тока, предполагая наличие только допантов *р*типа и их полную ионизацию, уравнение (61) упрощается до

$$\rho(y) = \begin{cases} -qN_A & (y < W_D), \\ 0 & (y \ge W_D). \end{cases}$$

(62)

Это приближение истощения — обычно достаточно неплохое и вместе с тем простое и позволяет получить аналитические решения.

Рисунок 14 показывает зонную диаграмму в режиме истощения и соответствующий ход электрического поля в n-MOSFET, которое получается в результате решения уравнения Пуассона:

$$\frac{dD}{dx} = \frac{d\left(\varepsilon_{S}E\right)}{dx} = \varepsilon_{S} \frac{dE}{dx} = \rho(y) = -qN_{A}, \quad \frac{dE}{dx} = \frac{-qN_{A}}{\varepsilon_{S}}.$$

(63)

Если плотность допирования однородная, тогда электрическое

**Рис. 14.** Иллюстрация эффекта истощения в n-MOSFET. Слева: зонная диаграмма. Справа: ход электрического поля внутрь подложки (пунктирная линия), а прямая линия соответствует приближению истощения.  $^{15}$

поле спадает в глубину подложки линейно с отрицательным наклоном (рис. 14, справа):

$$E(y) = \frac{qN_A}{\varepsilon_S} (W_D - y). \tag{64}$$

Важной величиной является электрическое поле на поверхности полупроводниковой подложки

$$\underline{E}|_{y=0} = E_S = \frac{qN_A}{\varepsilon_S} W_D.$$

(65)

Электростатический потенциал определяется через электрическое поле, а именно:

$$\psi(y) = -\int_{-\infty}^{y} E(y')dy'. \qquad (66)$$

Падение потенциала на протяжении всей области истощения  $\psi_s$  (рис. 14, слева) есть площадь под кривой  $E(y) \propto y$ , а именно:

$$\psi_S = \frac{1}{2} E_S W_D, \qquad (67)$$

откуда, используя (65), получаем важный результат:

$$W_D = \sqrt{\frac{2\varepsilon_s \psi_S}{qN_A}} \ . \tag{68}$$

Полный заряд в полупроводниковой подложке

$$Q_{S} = \int_{0}^{\infty} \rho(y) dy \approx Q_{D} = -q N_{A} W_{D} = \varepsilon_{s} E_{S} [K/M^{2}], \qquad (69)$$

а из (68) и (69) получаем ещё один важный результат:

$$Q_D \approx -\sqrt{2qN_A \, \varepsilon_s \psi_S} \ . \tag{70}$$

Обратим внимание, что в режиме истощения полный заряд в подложке  $Q_S$  практически совпадает с зарядом в слое истощения  $Q_D$ .

Когда полупроводниковая подложка транзистора путём подачи напряжения переведена в режим истощения, подробно рассмотренный выше, приближение истощения в теории MOSFET обеспечивает достаточно точные решения как для распределения электростатического потенциала, так и электрического поля. Мы рассматривали подложку p-типа. Соответствующие уравнения легко записать и для подложки n-типа. Однако, не всё так просто с режимами накопления и инверсии.

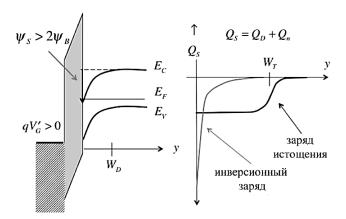

Инверсия. Рисунок 15 показывает зонные диаграммы и изменение заряда в условиях инверсии: большой потенциал  $\psi_S$  изгибает зону проводимости у поверхности раздела очень близко к уровню Ферми (рис. 15, слева), так что концентрация электронов у поверхности становится значительной (рис. 15, справа). Связь между концентрациями электронов у поверхности и в глубине подложки даётся выражением (58).

Зададимся вопросом: каким должен быть потенциал  $\psi_S$ , чтобы область под поверхностью раздела была n-типа, а в глубине подложки — p-типа? Из уравнения (58)

**Рис. 15.** Режим инверсии в полупроводнике. Слева: зонная диаграмма. Справа: ход заряда внутрь подложки. Инверсионный заряд резко возрастает вблизи поверхности раздела. <sup>16</sup>

$$\underline{n_0}\big|_{y=0} = \frac{n_i^2}{N_A} e^{+q\psi_S/kT} = N_A$$

(71)

получаем ответ:

$$\psi_S = 2\psi_B, \ \psi_B = \frac{kT}{q} \ln\left(\frac{N_A}{n_i}\right).$$

(72)

Уравнение (72) подводит итог инверсии: для потенциалов  $\psi_S$ , бо́льших  $2\psi_B$ , вблизи поверхности раздела диэлектрика с полупроводником p-типа реализуется слой n-типа. Итак, напряжение на затворе, создающее потенциал  $\psi_S$ , превосходящий  $2\psi_B$ , приводит к появлению канала проводимости n-типа, соединяющего области n-типа S и D и переводящего транзистор в режим «ON». Напряжение на затворе, необходимое для создания такого поверхностного потенциала  $\psi_S$ , и есть пороговое напряжение.

В условиях инверсии область истощения достигает глубины (рис. 15, справа)

$$W_{T} = W_{D} \left( 2\psi_{B} \right) = \sqrt{\frac{2\varepsilon_{s} \left( 2\psi_{B} \right)}{qN_{A}}}. \tag{73}$$

Полный заряд на единицу поверхности в области истощения

$$Q_D = -qN_AW_T [K/M^2]. (74)$$

Есть также значительный заряд, вызванный электронами инверсионного слоя, которые концентрируются вблизи поверхности раздела  $SiO_2$ -p-Si,

$$Q_n = q \int_0^\infty n_0(y) dy \ [\text{K/M}^2]. \tag{75}$$

Таким образом, полный заряд в полупроводнике в условиях инверсии (рис. 15, справа) есть

$$Q_{\rm S} = Q_{\rm D} + Q_{\rm n} \,. \tag{76}$$

Ток в MOSFET проводит только инверсионный слой. Позже мы установим связь между зарядом в инверсионном слое и напряжением на затворе.

Влияние подложки. До сих пор мы изучали электростатику MOS в середине достаточно длинного канала проводимости, где побочные электрические поля, создаваемые p-n-переходами, были малы, так что рассмотрения 1D-электростатики казалось достаточным. Но даже в этом случае p-n-переходы оказывают существен-

**Рис. 16.** Зона проводимости вдоль канала на поверхности подложки (y=0) от истока до стока. Сплошная линия соответствует условию плоских зон в подложке. Точечная линия соответствует поверхностному потенциалу  $\psi_S>0$ , а пунктирная линия соответствует  $\psi_S=2\psi_B$ . 17

ное влияние, иллюстрацией чего может служить рис. 16.

Высота барьера в условиях нулевых напряжений на терминалах транзистора есть просто  $qV_{bi}$ , где встроенный потенциал (built-in potential) p-n-переходов в стандартной теории полупроводников [6, 7] даётся выражением

$$V_{bi} = \frac{kT}{q} \ln \frac{N_A N_D}{n_i^2} \,. \tag{77}$$

Этот энергетический барьер — значительный, так что лишь считанные электроны со стороны как истока, так и стока могут его преодолеть.

Пунктирная линия на рис. 16 соответствует поверхностному потенциалу  $\psi_S = 2\psi_B$  . Барьер понижается до

$$E_b = q\left(V_{bi} - 2\psi_B\right) = kT \ln \frac{N_D}{N_A}. \tag{78}$$

Для типичных значений  $N_{\scriptscriptstyle D}=10^{20}~{\rm cm}^{-3}$  и  $N_{\scriptscriptstyle A}=10^{18}~{\rm cm}^{-3}$  пониженный барьер  $E_{\scriptscriptstyle b}\approx 0$ ,1 эВ. Электроны из истока могут преодолеть этот весьма небольшой барьер и уйти в инверсионный слой.

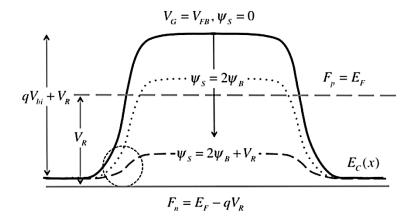

Теперь рассмотрим ситуацию на рис. 17, которая показывает зонные диаграммы, когда на исток и сток подано положительное напряжение, напряжение обратного смещения (reverse bias)  $V_{\rm g}$ .

В условии плоских зон (сплошная линия) высота барьера увеличивается до  $q(V_{bi}+V_R)$ . Точечная линия соответствует зонной диаграмме для  $\psi_S=2\psi_B$ , началу инверсии (рис. 16). В этом случае, однако, барьер всё ещё большой, и электроны не могут войти ни в исток, ни в

**Рис. 17.** Зона проводимости вдоль канала на поверхности подложки (y=0) от истока до стока при подаче напряжения обратного смещения  $V_R$  между S и D и подложкой B. Сплошная линия соответствует условию плоских зон в подложке. Точечная линия соответствует поверхностному потенциалу  $\psi_S = 2\psi_B$ , а пунктирная линия соответствует  $\psi_S = 2\psi_B + V_B$ . <sup>18</sup>

сток. Получить такой же небольшой барьер, как на рис. 16, можно при поверхностном потенциале  $\psi_S=2\psi_B+V_R$  (пунктирная линия). Полезно показать также ход зон вглубь полупроводниковой под-

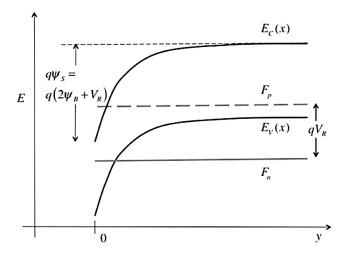

Полезно показать также ход зон вглубь полупроводниковой подложки, в направлении оси y (рис. 17), а не по ходу канала проводимости (в направлении оси x) как показано выше. Результаты для поверхностного потенциала  $\psi_S = 2\psi_B + V_R$  показаны на рис. 18.

Обратим внимание, что дырочный квазифермиевский уровень  $F_p$  (пунктирная линия на рис. 18) расположен там, где был уровень Ферми при нулевом напряжении на истоке и стоке, а при подаче напряжения обратного смещения квазифермиевский уровень для электронов понижается на  $qV_R$ . Электронный квазифермиевский уровень контролирует плотность электронов в полупроводнике. Для достижения той же электронной плотности при наступлении инверсии, как и в случае при  $V_R = \mathbf{0}$ , зоны должны изогнуться вниз дополнительно на величину  $qV_R$ .

Для создания инверсионного слоя на истоке канала проводимости зоны должны изогнуться вниз на  $q(2\psi_B + V_R)$ . Причина роста порогового напряжения связана с увеличением заряда истощения. Из (79) следует:

$$Q_D \approx -\sqrt{2qN_A \, \varepsilon_s \psi_S} = -\sqrt{2qN_A \, \varepsilon_s \left(2\psi_B + V_R\right)} \,. \tag{79}$$

Подача напряжения обратного смещения на исток существенно увеличивает заряд в слое истощения при входе в режим инверсии.

Наконец, можно задать вопрос, почему мы продолжаем считать полупроводник находящимся в равновесии, если p-n-

**Рис. 18.** Ход энергии зон вглубь полупроводниковой подложки для локации посередине канала проводимости при подаче напряжения обратного смещения  $V_R$  между S и D и подложкой B. Графики соответствуют случаю  $\psi_S = 2\psi_B + V_R$  на рис. 17. Обращает на себя внимание расщепление между квазифермиевскими уровнями при подаче  $V_R$ : электронный уровень понижается на величину  $qV_R$ . 19

переходы подавлены. Ответ состоит в том, что в режиме подачи напряжения обратного смещения или даже при подаче малого прямого смещения электрический ток настолько мал, что естественно считать полупроводник всё ещё в состоянии равновесия, не допуская при этом сколь-нибудь серьёзных ошибок.

Проиллюстрируем численно некоторые полученные результаты на примере кремния:  $N_A=1\cdot 10^{18}~{\rm cm}^{-3},~N_V=1,8\cdot 10^{19}~{\rm cm}^{-3},~n_i=1\cdot 10^{10}~{\rm cm}^{-3},~\epsilon_S=1,1,~T=300~{\rm K}.$

Ответим на следующие пять вопросов.

1) Где находится уровень Ферми в кремниевой подложке (*B*)? Перефразируя вопрос, определяем, насколько высоко над валентной зоной находится фермиевский уровень. Ответ следует из

$$p_{0B}=N_A=N_V e^{(E_v-E_p)/kT} \Rightarrow E_F-E_V=kT\lnrac{N_V}{N_A}=0,075$$

əB.

Положение уровня Ферми иначе можно определить относительно собственного уровня энергии  $E_i$ :

$$p_{0B}=N_{A}=n_{i}e^{(E_{i}-E_{F})/kT} \Rightarrow E_{i}-E_{F}=kT\lnrac{N_{V}}{n_{i}}=0,48$$

9B.

2) Каков поверхностный потенциал  $\psi_S$  при входе в режим инверсии? Ответ:  $\psi_S = 2\psi_B$ , и

$$\psi_B = \frac{kT}{q} \ln \frac{N_A}{n_i} = 0,48 \text{ B}, \ \psi_S = 0,96 \text{ B}.$$

(80)

В массивной подложке уровень Ферми расположен очень близко к валентной зоне. Чтобы сделать область под поверхностью подложки n-типа, в то время как сама подложка p-типа, нужно зону проводимости изогнуть вниз как можно ближе к уровню Ферми, т.е. изогнуть вниз практически на величину энергии запрещённой зоны ( $\approx 1$  эВ).

3) Какова глубина слоя истощения при входе в режим инверсии? Ответ:

$$W_{T}=\sqrt{4arepsilon_{s}\psi_{B}/qN_{A}}=36$$

HM.

4) Каков полный поверхностный заряд  $Q_D$  в слое истощения? Ответ:

$$Q_D = -qN_AW_T = -\sqrt{2q\,\epsilon_s N_A \left(2\psi_B\right)} = -5,8\cdot 10^{-6} \text{ K/cm}^2$$

(81)

или через плотность заряда —

$$|Q_n|/q = 3,6 \cdot 10^{12} \text{ [cm}^{-2]}.$$

5) Каково электрическое поле на поверхности подложки? Ответ:

$$E_{\rm S} = - Q_{\rm D} / \varepsilon_{\rm s} = 5, 6 \cdot 10^6 \, {\rm B/cm}.$$

Поле достаточно сильное.

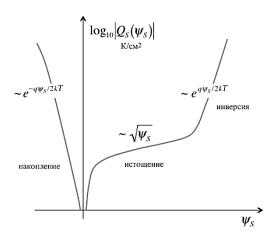

Обсудим заряд в полупроводнике и изгиб зон. Мы выше рассматривали, каким образом изгиб зон (поверхностный потенциал  $\psi_S$ ) контролирует заряд в полупроводнике. Рисунок 12 показывает изгиб зон в режимах накопления и истощения/инверсии, а рис. 19 демонстрирует, что в режиме накопления дырочный заряд мажоритарных носителей растёт экспоненциально с увеличивающимся отрицательным  $\psi_S$ . В области истощения, как видно из уравнения (70), заряд  $|Q_S| \propto \sqrt{\psi_S}$ . В области инверсии электронный заряд миноритарных носителей растёт экспоненциально с увеличивающимся положительным  $\psi_S > 2\psi_B$ .

Позже мы получим приближенные решения уравнения Пуассона-Больцмана для режимов накопления и инверсии, но ход  $Q_S\left(\psi_S\right)$  в целом уже не сложно представить.

Приведём критерии для слабой, умеренной и сильной инверсии. Ранее было установлено, что для режима инверсии характерно  $\psi_S > 2\psi_B$ , однако режим инверсии устанавливается постепенно. Заметим, что при  $\psi_S = \psi_B$  полупроводник на поверхности

**Рис. 19.** Ход заряда в полупроводнике p-типа с изменением поверхностного потенциала.  $^{20}$

беспримесный:  $n_0(0)=p_0(0)$ . При  $\psi_S>\psi_B$  на поверхности есть небольшой избыток электронов. Мы увидим позже, что эта небольшая избыточная концентрация электронов является причиной тока поверхностной утечки. Принято считать, что  $\psi_S=\psi_B$  есть критерий начала слабой инверсии.

При  $\psi_S=2\psi_B$  подповерхностный слой уже n-типа, тогда как подложка — p-типа; однако в этом подповерхностном слое концентрация электронов всё ещё невелика. Принято считать, что критерий  $\psi_S=2\psi_B$  означает конец слабой инверсии и начало умеренной инверсии.

Мы позже увидим, что режим  $I_{\rm ON}$  начинается с превышения  $2\psi_B$  всего на несколько kT/q. Когда поверхностный потенциал  $\psi_S$  становится немного больше  $2\psi_B$ , заряд  $Q_n >> Q_D$ : заканчивается умеренная инверсия и начинается сильная инверсия. Нам в дальнейшем не потребуются более строгие критерии инверсии, однако, дизайнерам и схемотехникам при моделировании MOSFET таковые исключительно важны [8].

Подведём итоги. Была рассмотрена традиционная теория MOSFET. Возникают, конечно, некоторые вопросы, например, какова роль истощения заряда в уравнении (8), характер тока при произвольном напряжении на стоке и т.п. [6-9], однако, существенные черты традиционного подхода вполне приемлемы и могут служить отправной точкой при разработке во многом совершенно иной физической картины процессов в нанотранзисторах.

Мы также переписали традиционную модель MOSFET в форме, близкой к модели виртуального истока нулевого уровня. Применение этой усовершенствованной модели к современным нанотранзисторам оказалось удивительно удачным, что является

следствием учёта электростатики MOS через такой существенный фактор как контроль высоты барьера между истоком и каналом со стороны затвора. Наиболее слабым местом этой модели является описание транспорта электронов, поскольку оно базируется на использовании таких понятий как подвижность и скорость насыщения. Именно поэтому эти две характеристики и были выбраны в качестве подгоночных параметров, с целью вписаться в экспериментальные данные для входных характеристик.

Далее мы вернёмся к более глубокому рассмотрению электростатики MOS и покажем, как более корректно можно описать подпороговую и надпороговую области, результатом чего явится улучшенная модель виртуального истока, однако, подвижность и скорость насыщения всё же останутся подгоночными параметрами. После этого мы физически более корректно опишем транспорт электронов и окончательно построим модель виртуального истока.

В основу настоящего обзора положены лекции Марка Лундстрома «Fundamentals of Nanotransistors» [15], прочитанные им в 2016 году в рамках инициативы Purdue University/nanohub.org/u.

#### ЦИТИРОВАННАЯ ЛИТЕРАТУРА-REFERENCES

- 1. S. R. Hofstein and F. P. Heiman, Proc. IEEE, 1190 (1963).

- 2. C. T. Sah, IEEE Trans. Electron Dev., 11: 324 (1964).

- 3. H. Shichman and D. A. Hodges, *IEEE J. Solid State Circuits*, SC-3: 285 (1968).

- 4. B. J. Sheu, D. L. Scharfetter, P.-K. Ko, and M.-C. Jeng, *IEEE J. Solid State Circuits*, SC-22: 558 (1987).

- I. M. Vikulin and V. I. Stafeev, Fizika Poluprovodnikovykh Priborov (Moscow: Radio i Svyaz': 1990) (in Russian); И. М. Викулин, В. И. Стафеев, Физика полупроводниковых приборов (Москва: Радио и связь: 1990).

- 6. R. F. Pierret, Semiconductor Device Fundamentals (New York: Addison-Wesley: 1996).

- 7. B. Streetman and S. Banerjee, *Solid State Electronic Devices* (New York: Prentice Hall: 2005).

- 8. Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor (New York: Oxford Univ. Press: 2011).

- 9. Y. Taur and T. Ning, Fundamentals of Modern VLSI Devices (New York: Oxford Univ. Press: 2013).

- 10. Yu. A. Kruglyak, Nanosistemi, Nanomateriali, Nanotehnologii, **16**, No. 2: 210 (2018) (in Russian); Ю. А. Кругляк, Наносистеми, наноматеріали, нанотехнології, **16**, вип. 2: 210 (2018).

- 11. C. G. Sodini, P.-K. Ko, and J. L. Moll, *IEEE Trans. Electron Dev.*, 31: 1386 (1984)

- 12. C. Geong, D. A. Antoniadis, and M. S. Lundstrom, *IEEE Trans. Electron Dev.*, **56**: 2762 (2009).

- 13. Y. Liu, M. Luisier, A. Majumdar, D. Antoniadis, and M. S. Lundstrom,

- IEEE Trans. Electron Dev., 59: 994 (2012).

- 14. A. Khakifirooz, O. M. Nayfeh, and D. A. Antoniadis, *IEEE Trans. Electron Dev.*, **56**: 1674 (2009).

- 15. M. Lundstrom, *Fundamentals of Nanotransistors* (Singapore: World Scientific: 2018); www.nanohub.org/courses/NT.

- 16. Chenming Hu, Modern Semiconductor Devices for Integrated Circuits (London: Pearson India: 2009).

- M. Lundstrom and Xingshu Sun, Notes on the Solution of the Poisson– Boltzmann Equation for MOS Capacitors and MOSFETs (West Lafayette, Indiana, USA: Purdue University: 2012); www.nanohub.org/resources/5338.

Odesa State Environment University, 15 Lvivska Str., UA-65016 Odesa, Ukraine

- <sup>1</sup> Fig. 1. Simplified presentation of n-Si MOSFET in the enrichment mode. The axis y is directed into the interior of the substrate, and the axis z is directed along the width of the conduction channel with an inversion charge since  $V_{GS} > V_T$ . The uniform  $(V_S = V_D = 0)$  distribution of the electron charge within the conduction channel connecting the n-doped terminals S and D from the channel beginning at the point x = 0 up x = L is shown.

- $^2$  Fig. 2. Long-channel MOSFET with indication of the pinched-off area. The variable depth of the channel in Figure illustrates the change in the charge density along the channel—the charge density is larger at the source origin and decreases as we approach the drain. The physical depth of the channel behaves in the opposite way: the depth of the channel rises from the source, where the gate field potential is greatest, to the drain, where the potential of the gate field is the smallest. The length of the channel, during which the charge density is significant, is L' < L.

- $^3$  Fig. 3. The output characteristics of the *n*-Si MOSFET, connected in the common source circuit, with  $L \approx 60$  nm. The characteristics are shown in 0.1 V steps, for the upper curve  $V_{GS} = 1.2$  V. It is noteworthy that for large  $V_{DS}$ , the current grows linearly with increasing gate voltage. This is a sign that there is velocity saturation in the channel [12].  $^4$  Fig. 4. The output characteristic of the *n*-MOSFET, connected in the common-source circuit,

- <sup>4</sup> Fig. 4. The output characteristic of the *n*-MOSFET, connected in the common-source circuit, at a certain gate voltage. The dashed lines give a current in the linear region and in the saturation region according to (28).

- Fig. 5. Accounting for the resistance of terminals S and D MOSFET. Left: an idealized MOSFET. Right: real MOSFET, showing the influence of the resistance of contacts S and D on the voltage in an idealized field-effect transistor.

- on the voltage in an idealized field-effect transistor.  $^6$  Fig. 6. The effect of taking into account the resistances of contacts S and D on the MOSFET VAC. The dashed line shows the input characteristic without taking into account the resistance of the contacts. Allowance for  $R_S$  and  $R_D$  resistances increases the resistance of the conduction channel and lowers the current  $I_{\rm ON}$ .

- $^7$  Fig. 7. Measured and calculated by the VS model of the VAC of a 32 nm n-MOSFET. Left: output characteristics of the MOSFET, connected in the common source circuit, in increments  $\Delta V_{GS} = 0.1\,$  V. Right: transfer characteristics. We used a higher-level VS model [14], which is equally suitable for both sub-threshold and over-threshold voltages, and is described in detail below.

- <sup>8</sup> Fig. 8. Selection of the y-axis direction into the depth of the semiconductor substrate (on the left) and the orientation of the conduction channel (from the bottom to the top) when displaying the zone diagrams (right).

- <sup>9</sup> Fig. 9. With a constant electrostatic potential, the zones are flat. The width  $E_G$  of the forbidden zone is shown.

- <sup>10</sup> **TABLE.** Values of  $N_C$  and  $N_V$  for Ge, Si and GaAs for 300 K·cm<sup>-3</sup>.

- <sup>11</sup> Fig. 10. The effect of positive voltage on the gate ( $V_{GS} > 0$ ) on the path of the electrostatic potential (left) and the bending of the zones (right).

<sup>12</sup> Fig. 11. Left: fulfilment of the condition of flat zones in the idealized MOS structure.

- <sup>12</sup> Fig. 11. Left: fulfilment of the condition of flat zones in the idealized MOS structure. Right: bending zones as a result of applying a positive voltage to the gate.

- sponds to the exhaustion approximation.

<sup>16</sup> Fig. 15. Mode of inversion in a semiconductor. Left: zone diagram. Right: the progress of the charge inside the substrate. The inversion charge sharply increases near the interface.

- <sup>17</sup> Fig. 16. The conduction band along the channel on the surface of the substrate (y=0) from the source to the drain. The solid line corresponds to the condition of flat zones in the substrate. The dotted line corresponds to the surface potential,  $\psi_S > 0$  and the dashed line corresponds to  $\psi_S = 2\psi_B$ .

- <sup>18</sup> Fig. 17. The conduction band along the channel on the surface of the substrate (y=0) from the source to the drain when the reverse bias voltage  $V_R$  is applied between S and D and the substrate B. The solid line corresponds to the condition of flat zones in the substrate. The dotted line corresponds to the surface potential,  $\psi_S = 2\psi_B$ , and the dashed line corresponds to  $\psi_S = 2\psi_B + V_B$ .

- $\psi_S=2\psi_B+V_R$ .

<sup>19</sup> Fig. 18. The course of the energy of the zones into the interior of the semiconductor substrate for locating in the middle of the conduction channel when the reverse bias voltage  $V_R$  is applied between S and D and the substrate B. The graphs correspond to the case  $\psi_S=2\psi_B+V_R$  in Fig. 17. Attention is drawn to the splitting between the quasi-Fermi levels during the supply of  $V_R$ : the electronic level decreases by an amount  $qV_R$ .

- <sup>20</sup> Fig. 19. The charge path in a p-type semiconductor with a change in the surface potential.

<sup>&</sup>lt;sup>13</sup> Fig. 12. The nature of the bending of the zones at three different gate voltages: accumulation of carriers (left,  $V_{GS} < 0$ ), depletion/inversion (right,  $V_{GS} > 0$ ), flat zones (centred,  $V_{GS} = 0$ ).

<sup>&</sup>lt;sup>14</sup> Fig. 13. The nature of the zone bending in the modes of accumulation, depletion and inversion, as well as in two transition locations—flat zones and threshold. The negative voltage on the shutter corresponds to the 'up' arrows, and the 'down' arrows indicate a positive voltage [16].

<sup>&</sup>lt;sup>15</sup> Fig. 14. Illustration of the depletion effect in the *n*-MOSFET. Left: zone diagram. Right: the course of the electric field inside the substrate (dashed line), and the straight line corresponds to the exhaustion approximation.